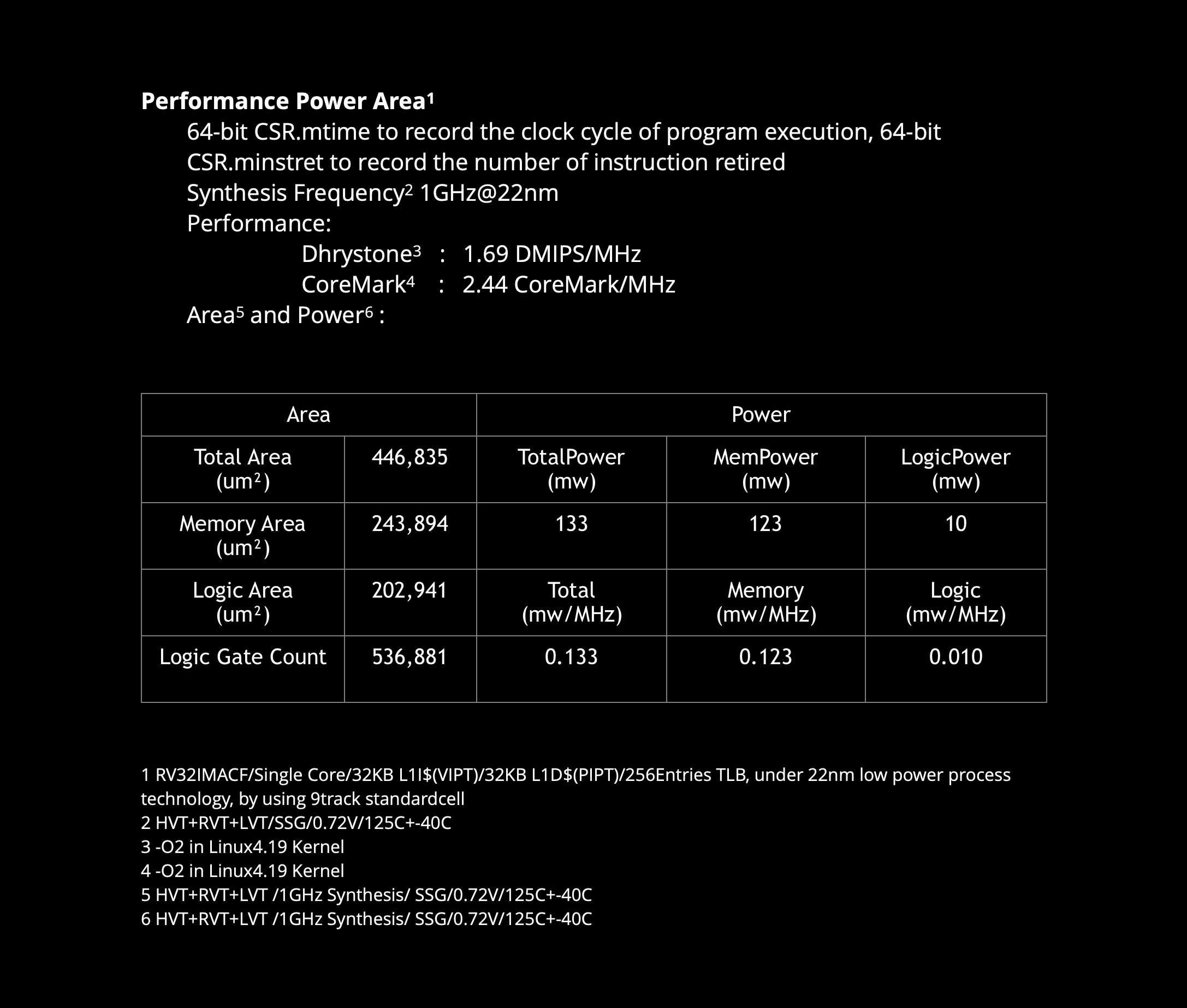

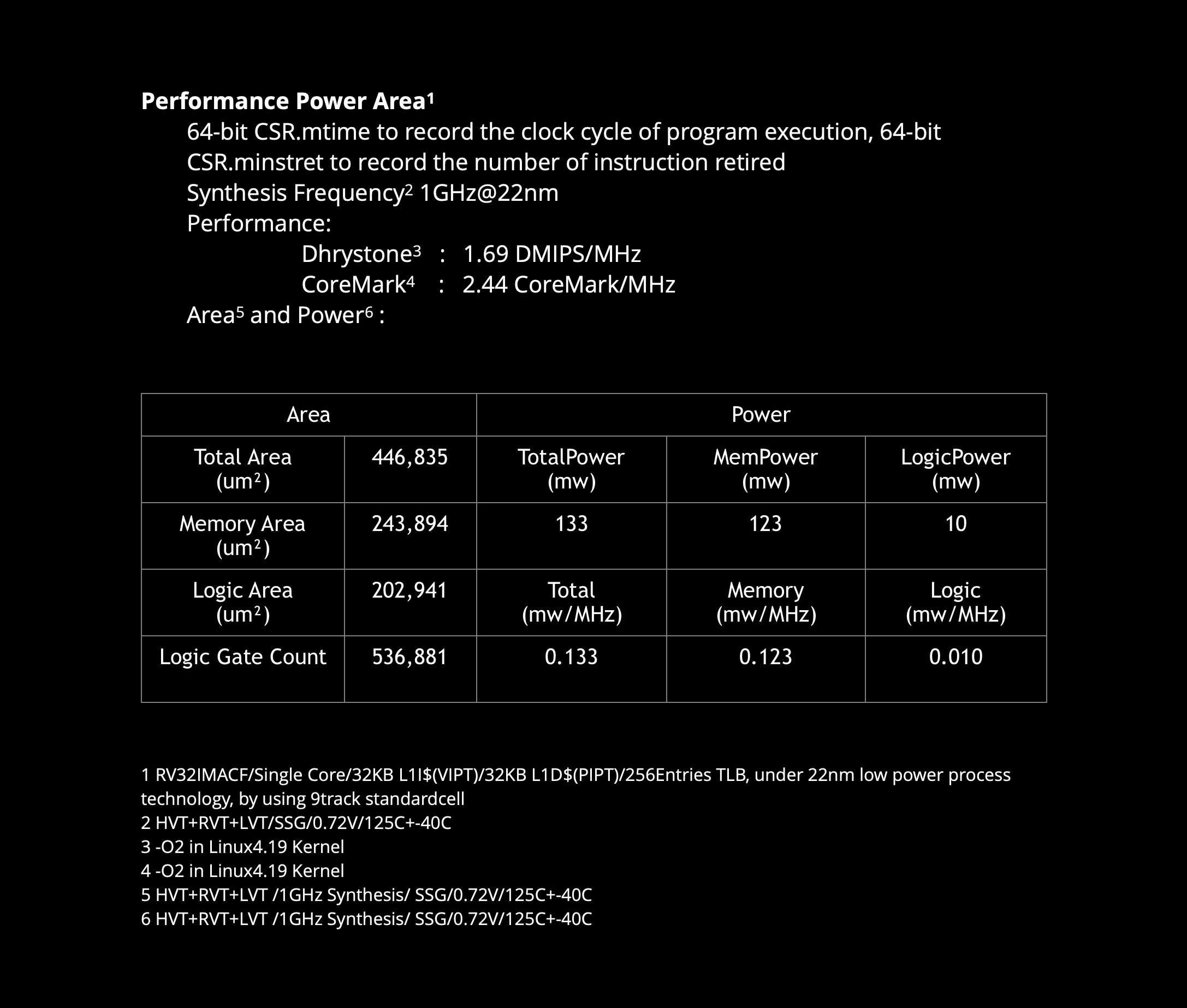

We provide high-quality silicon-proven RISC-V compatible processor IP core, verification suite, software and toolchains.

We provide comprehensive benchmarking and competitive analysis reports e.g. EEMBC and field application silicon and system measurement results.

We deliver satisfactory time-to-market product development and professional design service, e.g. it took one month and a half time-frame from kickoff to launch the project to customer’s silicon tape-out successfully on December, 2018

We secure one-pass-success project development under a high-quality and silicon-proven development and QA process.

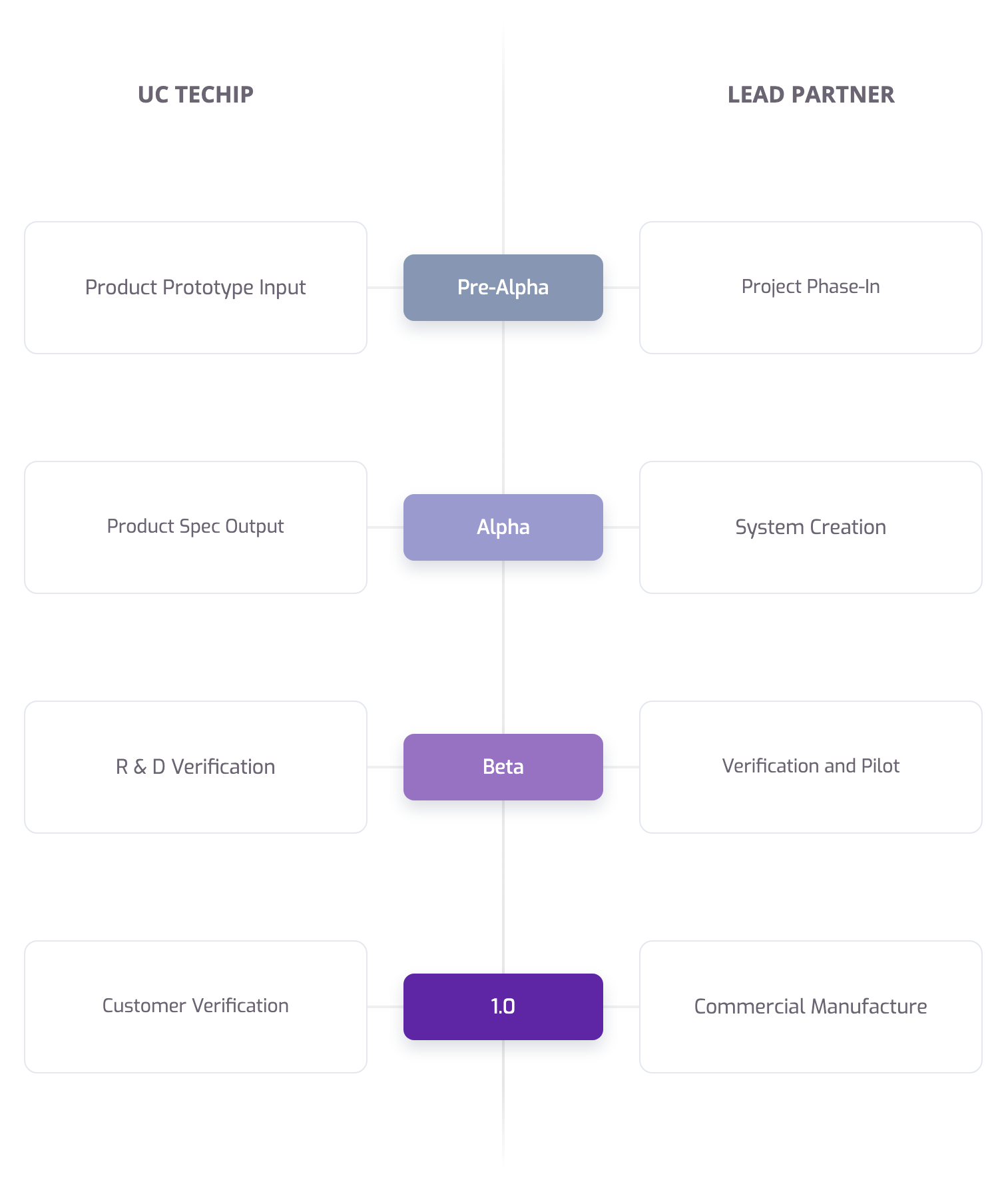

product development and quality management

UC Techip

Lead Partner

Product Prototype Input

Project Phase-In

Product Spec Output

System Creation

R & D Verification

Verification and Pilot

Customer Verification

Commercial Manufacture

- WH32 (single-core and multi-core)

- WH64

- LDJ32HPC

WH32

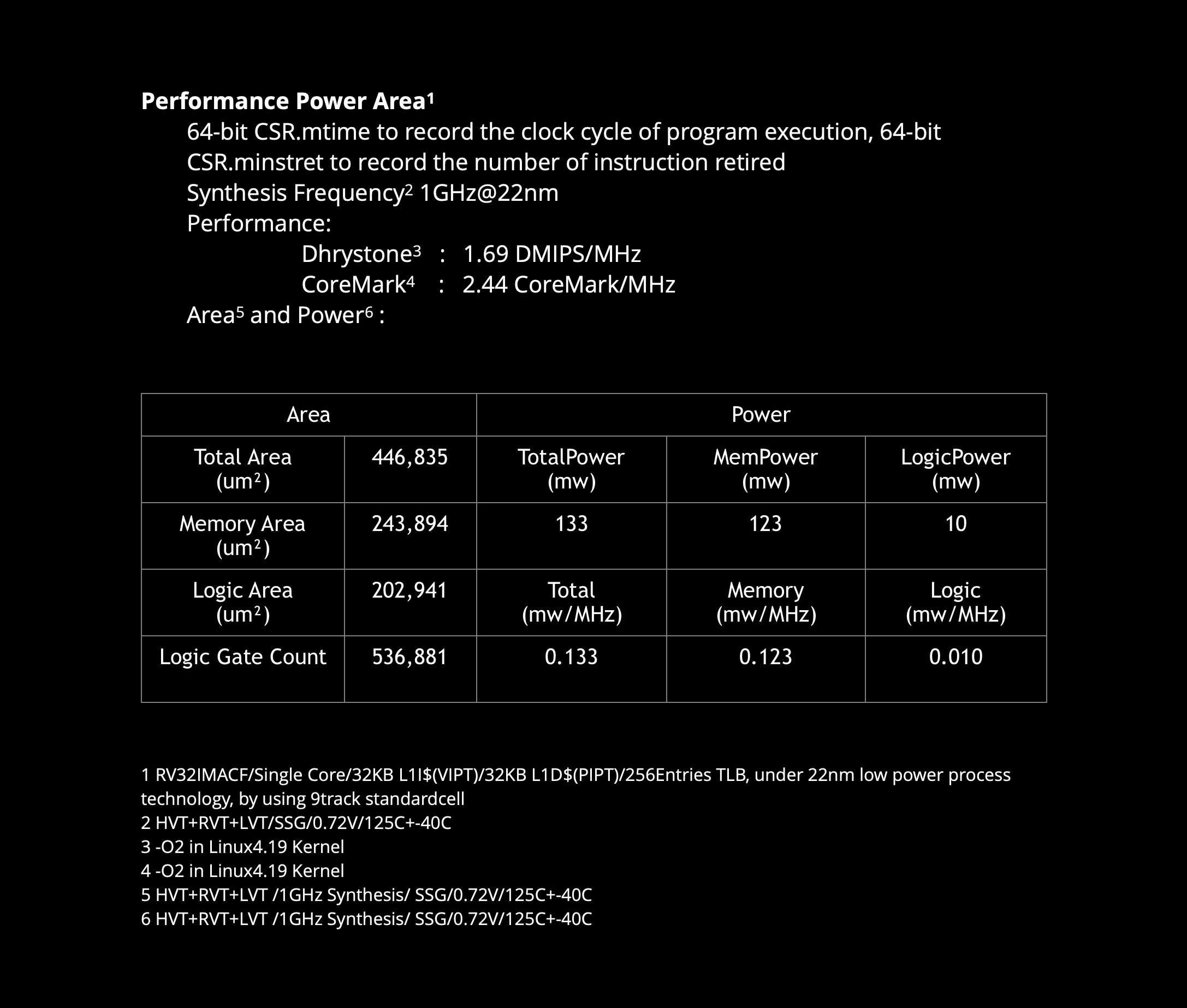

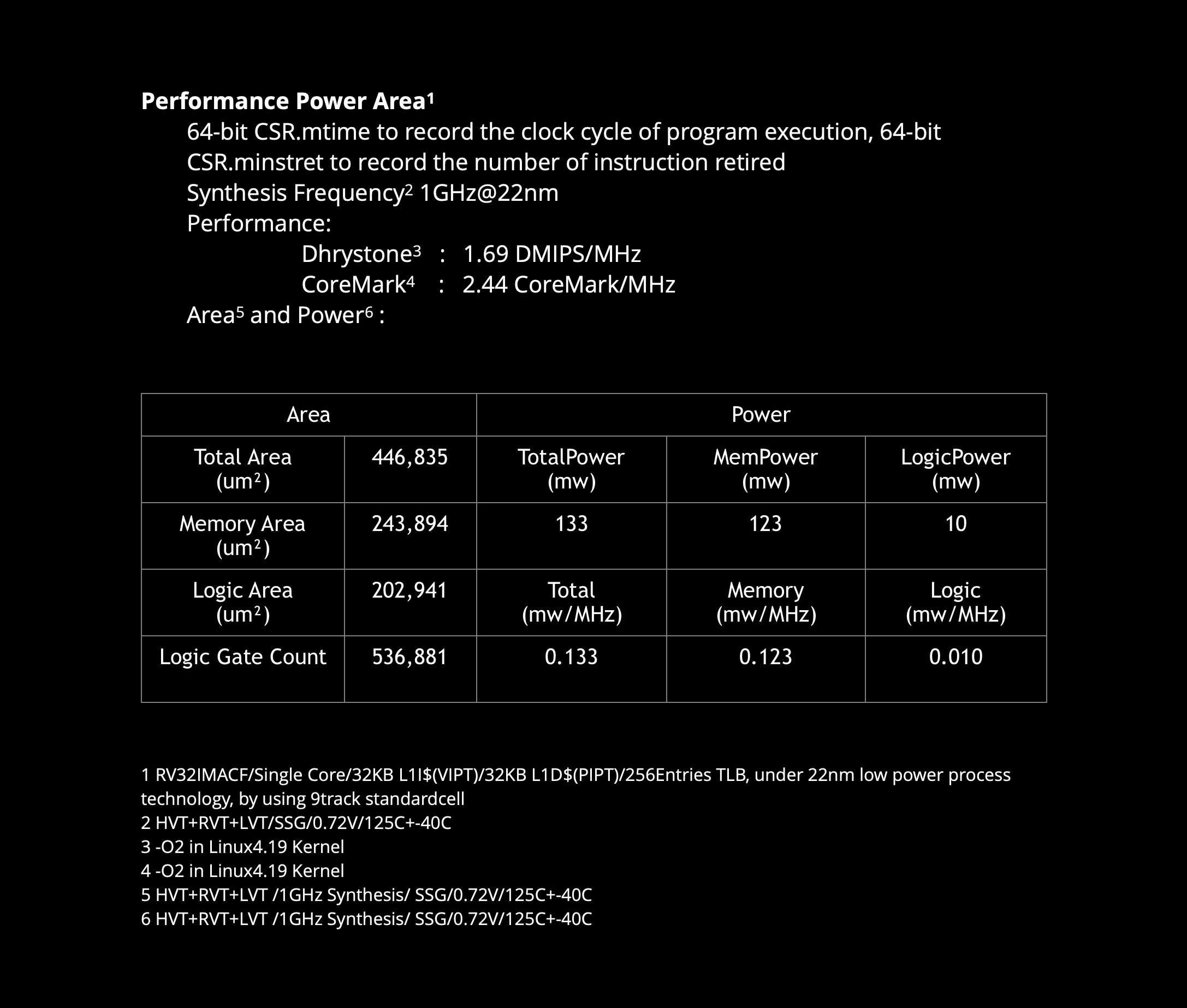

WH32 is a Silicon-Proven 32-bit High-Performance Low-Power Processor IP Core

- uBright Instruction Set Architecture (ISA) compatible with RISC-V architecture

- 1-4 Cores Cluster, 5-stage integer pipeline, 6-stage floating -point pipeline

- Support 32-bit RISC-V [I|M|A|C|F] Instruction Set

- Machine/Supervisor/User Mode

- 4K-64K ICache & DCache

- Dynamic branch prediction to speed up control instruction flow code

- Return Address Stack (RAS) to speed up procedure returns

- Support up to 16 Physical Memory Protection (PMP)

- Support 1-256 Platform Level Interrupt

- Support Virtual Memory Architecture (sv32)

- The CPI for most basic instructions is 1 cycle/inst

- mul may have 3-5 cycle latency

- div may have 3-33 cycle latency

- load may have 2-3 cycle latency if cache hit

- atomic may have 6-7 cycle latency

- 16/32 bit mixable instruction format for compacting code density

- Custom Extension Instruction Interface for customized accelerator

- Support Hardware Performance Counter

- Both RTOS & Linux OS supported

Application

- Audio/Video signal processing

- Artificial Intelligence acceleration

- Computer Vision and Pattern Recognition

Development Environment

- LS-Extended SoC Development Platform

- Eclipse IDE w/i GNU Toolchains

- GDB + OpenOCD

- Loader: JLINK/FT2232/Olimex

- RTOS

- Linux

- IDE and Profiling, Trace and Debugger, Simulator

- ISA analysis and DSA design

- SPEC2GDSII

- Software development

- eFPGA data-acceleration and Chiplet design

UC Techip is a technology R&D and service provider with forward innovation and delivery to open ISA, RISC-V based processor core and verification suite, software, silicon intellectual property (IP) and Domain Specific Architecture (DSA) solution. Joined RISC-V Foundation on 2017, UC Techip has offices at Santa Clara, California and China Xi'an, and Shenzhen.

Thanks to RISC-V Foundation and Partnership